香港中文大學

The Chinese University of Hong Kong

## CENG3430 Rapid Prototyping of Digital Systems Lecture 01: Introduction to VHDL

### Ming-Chang YANG

mcyang@cse.cuhk.edu.hk

## Outline

- Basic Structure of a VHDL Module

- ① Library Declaration

- ② Entity Declaration

- ③ Architecture Body

- Data Objects, Identifiers, Types, and Attributes

- Data Objects

- ① Constant

- ② Signal

- ③ Variable

- Data Identifier

- Data Types

- Data Attributes

- Operators in VHDL

# **Basic Structure of a VHDL Module**

### A VHDL file

### **Library Declaration**

library IEEE; use IEEE.std\_logic\_1164.all; use IEEE.std\_logic\_arith.all; use IEEE.std\_logic\_unsigned.all;

### **Entity Declaration**

Define the <u>signals</u> to be seen outside <u>externally</u> (I/O pins)

### Architecture Body Define the internal operations of the entity (desired functions)

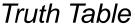

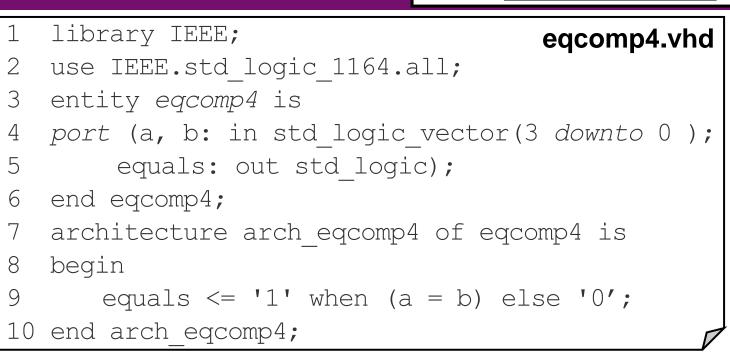

# Example: 4-bit Comparator in VHDL (1/2)

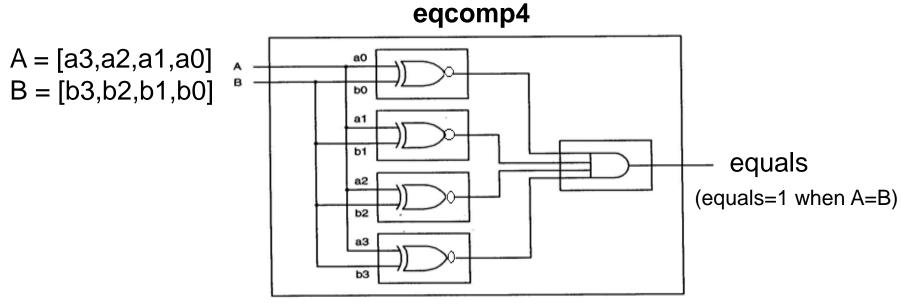

• Schematic Circuit of a 4-bit Comparator

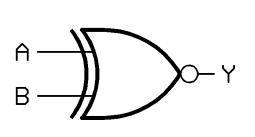

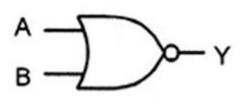

\*Recall: Exclusive NOR (XNOR)

- When A=B, Output Y = 0

- Otherwise, Output Y = 1

| A | В | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

VHDL for programmable logic, Skahill, Addison Wesley

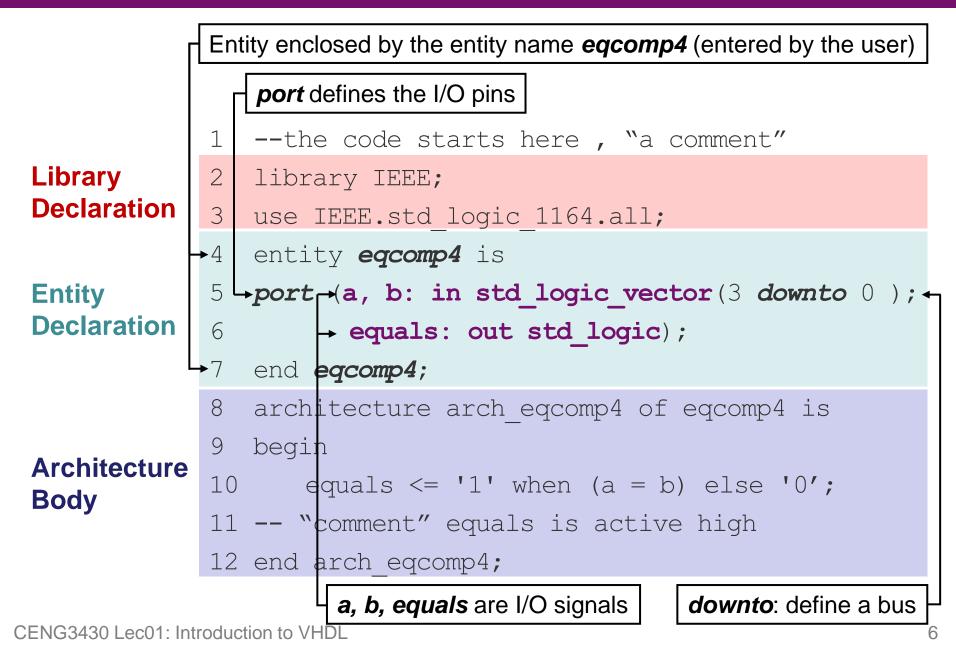

# Example: 4-bit Comparator in VHDL (2/2)

Code of 4-bit Comparator in VHDL:

| eqcomp4.vh           | d  |                                                          |

|----------------------|----|----------------------------------------------------------|

|                      | 1  | the code starts here , "a comment"                       |

| Library              | 2  | library IEEE;                                            |

| Declaration          | 3  | use IEEE.std_logic_1164.all;                             |

|                      | 4  | entity eqcomp4 is                                        |

| Entity               | 5  | <pre>port (a, b: in std_logic_vector(3 downto 0 );</pre> |

| Declaration          | 6  | equals: out std_logic);                                  |

|                      | 7  | end eqcomp4;                                             |

|                      | 8  | architecture arch_eqcomp4 of eqcomp4 is                  |

| Anchitesture         | 9  | begin                                                    |

| Architecture<br>Body | 10 | equals <= '1' when $(a = b)$ else '0';                   |

| Dody                 | 11 | "comment" equals is active high                          |

|                      | 12 | end arch_eqcomp4;                                        |

|                      |    | $\square$                                                |

# **Entity Declaration**

# I/O Signals

- An I/O signal (or I/O pin) can

- Carry logic information.

- Be implemented as a wire in hardware.

- Be "in", "out", "inout", "buffer" (modes of I/O pin)

- There are many logic types of signals

- 1) bit: can be logic 1 or 0 only

- 2) std\_logic: can be 1, 0, Z (high impedance), ..., etc

- Standard logic (an IEEE standard)

- 3) std\_logic\_vector: a group of wires (a bus)

- a, b: in std\_logic\_vector(3 downto 0); in VHDL

- a(0), a(1), a(2), a(3), b(0), b(1), b(2), b(3) are **std\_logic** signals

# **Class Exercise 1.1**

| Student | ID: |

|---------|-----|

| Name:   |     |

Date:

- How many input and output pins are there in the code? Answer: \_\_\_\_\_\_

- What is the difference between std\_logic and std\_logic\_vector? Answer:

| lace Evereise 1 7                   | Name:     |

|-------------------------------------|-----------|

| 1 entity test12 is                  | test1.vhd |

| 2 port (in1, in2: in std_logic;     |           |

| 3 out1: out std_logic);             |           |

| 4 end test12;                       |           |

| 5 architecture test12arch of test12 | is        |

| 6 begin                             |           |

| 7 outl <= inl or in2;               |           |

| 8 end test12_arch;                  |           |

Student ID.

- Draw the schematic chip and names the pins.

Answer:

CENG3430 Lec01: Introduction to VHDL

Data:

# Modes of I/O Pins

Modes of I/O pin should be <u>explicitly specified</u> in port of entity declaration:

Example:

```

entity do_care is port(

```

- s: in std\_logic\_vector(1 downto 0);

- y: **buffer** std\_logic);

end do care;

- There are 4 modes of I/O pins:

- 1) in: Data flows in only

- 2) out: Data flows out only (cannot be read back by the entity)

- 3) inout: Data flows bi-directionally (i.e., in or out)

- 4) buffer: Similar to out but it can be read back by the entity

## **Class Exercise 1.3**

| Student | ID: |

|---------|-----|

| Name:   |     |

Date:

- Based on the following schematic, identify the modes of the IO pins.

# Architecture Body (More in Lec03)

- Architecture Body: Defines the operation of the chip Example:

- architecture arch\_eqcomp4 of eqcomp4 is begin

- equals <= '1' when (a = b) else '0';

- -- "comment" equals is active high

- end arch\_eqcomp4;

How to read it?

- arch\_eqcomp4: the architecture name (entered by the user)

- equals, a, b: I/O signal pins designed by the user in the entity declaration

- **begin** ... **end**: define the internal operation

- equals <= '1' when (a = b) else '0';

- "--": comment

## **Class Exercise 1.4**

| Student ID: | 1 |

|-------------|---|

| Name:       |   |

Date:

- Draw the schematic circuit for the following code.

- 1 library IEEE;

- 2 use IEEE.STD\_LOGIC\_1164.ALL;

- 3 entity test is

- 4 port( in1: in std\_logic\_vector (2 downto 0);

- 5 out1: out std\_logic\_vector (3 downto 0));

- 6 end test;

- 7 architecture test\_arch of test is

8 begin

9 out1(0) <= in1(1);

```

10 out1(1) <= in1(2);

```

11 out1(2) <= not(in1(0) and in1(1));

```

12 out1(3) <= '1';

```

```

13 end test_arch ;

```

## Outline

- Basic Structure of a VHDL Module

- ① Library Declaration

- ② Entity Declaration

- ③ Architecture Body

- Data Objects, Identifiers, Types, and Attributes

- Data Objects

- ① Constant

- ② Signal

- ③ Variable

- Data Identifier

- Data Types

- Data Attributes

### Operators in VHDL

# **Objects: 3 Different Data Objects**

- Data objects are assigned types and hold values of the specified types.

- Data objects belong to one of three classes:

- 1) Constants (Globla): Hold unchangeable values

- E.g., constant width: INTEGER := 8;

- 2) Signals (Globla): Represent physical wires

- E.g., signal count: BIT := `1';

- 3) Variables (Local): Used only by programmers for internal representation (less direct relationship to the synthesized hardware)

- E.g., variable flag: BOOLEAN := TRUE;

- Data objects must be declared before being used.

constant CONST\_NAME: <type> := <value>;

Note: Constants must be declared with initialized values.

- Examples:

- constant CONST\_NAME: STD\_LOGIC := 'Z';

- constant CONST\_NAME: STD\_LOGIC\_VECTOR (3

downto 0) := "0-0-";

- `-' is don't care

- Constants can be declared in

- Anywhere allowed for declaration.

### signal SIG\_NAME: <type> [: <value>];

Note: Signals can be declared without initialized values.

- Examples:

- signal s1\_bool: BOOLEAN;

- Declared without initialized value

- signal xsl\_int1: INTEGER := 175;

- signal su2\_bit: BIT := `1';

- Signals can be declared

- Either in the "port" of the entity declaration,

- Or before the "begin" of the architecture body.

# **Recall: Modes of I/O Pins**

- If a signal is declared in port, it is used as I/O pins.

- Modes of I/O pin should be <u>further explicitly specified</u> in **port** of entity declaration:

Example:

entity do\_care is port(

- s: in std\_logic\_vector(1 downto 0);

- y: **buffer** std\_logic);

end do\_care;

- There are 4 modes of I/O pins:

- 1) in: Data flows in only

- 2) out: Data flows out only (cannot be read back by the entity)

- 3) inout: Data flows bi-directionally (i.e., in or out)

4) buffer: Similar to out but it can be read back by the entity CENG3430 Leco1: Introduction to VHDL

variable VAR\_NAME: <type> [: <value>];

Note: Variables can be declared without initialized values.

- Examples:

- variable v1 bool: BOOLEAN:= TRUE;

- variable val int1: INTEGER:=135;

- variable vv2 bit: BIT;

- Declared without initialized value

- Variables can only be declared/used in the process statement in the architecture body (see Lec03).

# Signals and Variables Assignments

- Both signals and variables can be declared without initialized values.

- Their values can be assigned after declaration.

- Syntax of signal assignment:

SIG NAME <= <expression>;

– Syntax of variable assignment:

VAR\_NAME := <expression>;

#### Student ID: \_\_\_\_\_ Date: **Class Exercise 1.5** Name: entity nandgate is 1 2 port (in1, in2: in STD LOGIC; 3 out1: out STD LOGIC); 4 end nandgate; 5 architecture nandgate arch of nandgate is 6 7 begin 8 connect1 <= in1 and in2; 9 out1<= not connect1; 10 end nandgate arch;

- Declare a signal named "connect1" in Line 6.

- Can you assign an I/O mode to this signal? Why? Answer:

- Where can we declare signals?

Answer: \_\_\_\_\_\_

- Draw the schematic circuit for the code.

# What we learnt so far

- Data Objects

- ① Constant

- ② Signal

- In Entity Declaration (Port): External I/O Pins

Modes of I/O Pins:

- 1) In

- ② Out

- ③ Inout

- ④ Buffer

- In Architecture Body: Internal Signals

### ③ Variable

## Outline

- Basic Structure of a VHDL Module

- ① Library Declaration

- ② Entity Declaration

- ③ Architecture Body

- Data Objects, Identifiers, Types, and Attributes

- Data Objects

- ① Constant

- ② Signal

- ③ Variable

- Data Identifier

- Data Types

- Data Attributes

- Operators in VHDL

## Outline

- Basic Structure of a VHDL Module

- Library Declaration

- Entity Declaration

- Architecture Body

- Data Objects, Identifiers, Types, and Attributes

- Data Objects

- ① Constant

- ② Signal

- ③ Variable

- Data Identifier

- Data Types

- Attributes

### Operators in VHDL

## **Identifiers**

- Identifiers: Used to represent and name an object

An object can be constant, signal or variable.

- Rules for naming data objects:

- 1) Made up of alphabets, numbers, and underscores

- 2) <u>First</u> character must be a <u>letter</u>

- 3) Last character CANNOT be an underscore

- 4) NOT case sensitive

- Txclk, Txclk, TXCLK, TxClk are all equivalent

- 5) <u>Two</u> connected <u>underscores</u> are NOT allowed

- 6) VHDL-reserved words may NOT be used

# **Class Exercise 1.6**

| Studen | t ID: |  |

|--------|-------|--|

| Name:  |       |  |

- Determine whether the following identifiers are legal or not. If not, please give your reasons.

- tx\_clk

- \_tx\_clk

- Three\_State\_Enable

- 8B10B

- sel7D

- HIT\_1124

- large#number

- link\_\_bar

- select

- rx\_clk\_

Date:

### Alias

- An alias is an <u>alternate identifier</u> for an existing object.

It is <u>NOT a new</u> object.

- Referencing the alias is equivalent to the original one.

- It is often used as a convenient method to identify a range of an array (signal bus) type.

- Example:

- signal sig\_x: std\_logic\_vector(31 downto 0);

- alias top\_x: std\_logic\_vector (3 downto 0)

is sig\_x(31 downto 28);

## Outline

- Basic Structure of a VHDL Module

- ① Library Declaration

- ② Entity Declaration

- ③ Architecture Body

- Data Objects, Identifiers, Types, and Attributes

- Data Objects

- ① Constant

- ② Signal

- ③ Variable

- Data Identifier

- Data Types

- Data Attributes

### Operators in VHDL

# **Data Types in VHDL**

- VHDL is strongly-typed language.

- Data objects of <u>different base types</u> CANNOT to assigned to each other without the use of type-conversion.

- A type has <u>a set of values</u> and <u>a set of operations</u>.

- Common types can be classified into two classes:

- Scalar Types

- Integer Type

- Floating Type

- Enumeration Type

- Physical Type

- Composite Types

- Array Type

- Record Type

# Scalar: Integer Type

- An integer type can be defined with or without specifying a range.

- If a range is not specified, VHDL allows integers to have a minimum rage of

-2,147,483,647 to 2,147,483,647

$-(2^{31}-1)$  to (231-1)

- Or a range can be specified, e.g.,

variable a: integer range 0 to 255;

# Scalar: Floating Type

- Floating point type values are used to <u>approximate</u> real numbers.

- The only predefined floating type is named REAL, which includes the range

-1.0E38 to + 1.0E38

- Floating point types are <u>rarely used</u> (or even <u>not supported</u>) in code to be <u>synthesized</u> (see Lec02).

- Because of its huge demand of resources.

# Scalar: Enumeration Type (1/2)

- How to introduce an abstract concept into a circuit?

- An enumeration type is defined by a list of values.

- The list of values may be defined by users.

- Example:

type colors is (RED, GREEN, BLUE);

signal my color: colors;

- Enumeration types are often defined for state machines (see Lec04).

- There are two particularly useful enumeration types predefined by the IEEE 1076/1993 standards.

- type BOOLEAN is (FALSE, TRUE);

- **type** BIT is ('0', '1');

# Scalar: Enumeration Type (2/2)

- An enumerated type is ordered.

- The order in which the values are listed in the type declaration defines their relation.

- The leftmost value is less than all other values.

- Each values is greater than the one to the left, and less than the one to the right.

- Example:

type colors is (RED, GREEN, BLUE)

signal my\_color: colors;

– Then a comparison of my\_color can be:

when my\_color >= RED

# Scalar: Physical Type

- Physical type values are used as measurement units.

- They are used mainly in simulations (see Lab01).

- The only predefined physical type is TIME.

- Its primary unit is fs (femtoseconds) as follows:

```

type time is range -2147483647 to 2147483647

units

```

```

fs;

ps = 1000 fs;

ns = 1000 ps;

us = 1000 ns;

ms = 1000 us;

sec = 1000 ms;

min = 60 sec;

hr = 60 min;

end units;

```

# **Composite: Array Type**

- An object of an array type consists of <u>multiple</u> elements of the <u>same</u> type.

- The most commonly used array types are those predefined by the IEEE 1076 and 1164 standards:

type BIT\_VECTOR is array (NATURAL range <>) of bit; type STD LOGIC VECTOR is array (NATURAL range <>) of std logic;

- Their range are not specified (using range <>), and only bounded by NATURAL (positive integers).

- Example:

port (a: in std\_logic\_vector (3 downto 0);

b: in std\_logic\_vector (0 to 3);

equals: out std\_logic);

- a, b are both 4-bit vectors of std\_logic.

# **Class Exercise 1.7**

| Student ID: |  |

|-------------|--|

| Name:       |  |

Date:

• Given

a: std\_logic\_vector (3 downto 0);

• Create a 4-bit bus c using "to" instead of "downto":

• Draw the circuit for this vector assignment  $\rm c~<=~a$

# **Composite: Record Type**

- An object of a record type consists of <u>multiple</u> elements of the <u>different</u> types.

- Individual fields of a record can be used by element name.

- Example:

- type iocell is **record**

- buffer\_in: bit\_vector(7 downto 0);

- bnable: bit;

- buffer\_out: bit\_vector(7 downto 0);

- end **record;**

- Then we can use the record as follows:

signal bus\_a: iocell; signal vec: bit\_vector(7 downto 0); bus\_a.buffer\_in <= vec;</pre>

# **Types and Subtypes**

- A subtype is a type with a constraint.

- Subtypes are mostly used to define objects based on existing base types with a constraint.

- Example:

- Without subtype

- signal my\_byte: bit\_vector(7 downto 0);

- With subtype:

subtype byte is bit\_vector(7 downto 0);

signal my\_byte: byte;

- Subtypes are also used to resolve a base type.

- A resolution function is defined by the IEEE 1164 standard. subtype std\_logic is resolved std\_ulogic;

- Resolved is the name of the resolution function.

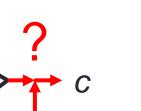

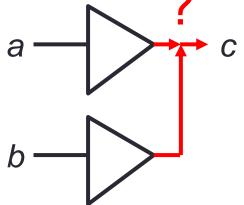

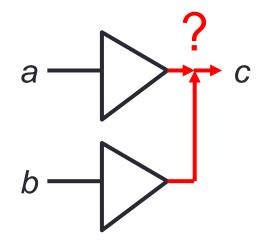

# **Resolved Logic Concept**

- Resolved Logic (Multi-value Signal): <u>Multiple outputs</u> can be connected together to drive a signal.

- The resolution function is used to determine how multiple values from different sources (drivers) for a signal will be reduced to one value.

- Single-value Signal Assignment: signal a, c: bit;

c <= a;</li>

- Multi-value Signal Assignment: signal a, b, c: bit;

← We need to "resolve" it!

CENG3430 Lec01: Introduction to VHDL

<= a;

46

## std\_logic vs. std\_ulogic (1/2)

- std\_logic: a type of resolved logic, that means a signal can be driven by 2 inputs.

- std\_ulogic ("u" means unresolved): a type of unresolved logic, that means a signal CANNOT be driven by 2 inputs.

# std\_logic vs. std\_ulogic (2/2)

How to use it?

library IEEE;

#### use IEEE.std\_logic\_1164.all;

entity

architecture

# **IEEE 1164: 9-valued Logic Standard**

- 'U': Uninitialized

- 'X': Forcing Unknown

- '0': Forcing 0

- '1': Forcing 1

- 'W': Weak Unknown

- 'L': Weak 0

- 'H': Weak 1

- 'Z': High Impedance (Float) '-': Don't care

|   |   |   | VH | DL Resolution Table |   |   |   |   |   |

|---|---|---|----|---------------------|---|---|---|---|---|

|   | U | x | 0  | 1                   | Z | W | L | H | _ |

| U | U | U | U  | U                   | U | U | U | U | U |

| х | U | Х | Х  | Х                   | Х | Х | Х | Х | Х |

| 0 | U | Х | 0  | Х                   | 0 | 0 | 0 | 0 | Х |

| 1 | U | Х | Х  | 1                   | 1 | 1 | 1 | 1 | Х |

| Z | U | Х | 0  | 1                   | Z | W | L | Н | Х |

| W | U | Х | 0  | 1                   | W | W | W | W | Х |

| L | U | Х | 0  | 1                   | L | W | L | W | Х |

| н | U | Х | 0  | 1                   | Н | W | W | Н | Х |

• Rule: When 2 signals meet, the forcing signal dominates.

# bit vs. std\_logic

• bit is a predefined type and can only represents the idealized value 0 or 1.

-type bit IS ('0', '1');

- std\_logic provides more realistic modeling of

signals within a digital system.

- -type std\_ulogic IS ( 'U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-');

- SUBTYPE std\_logic IS resolved std\_ulogic;

- Type-conversion functions (i.e., to\_bit & to\_std\_logic) are needed for the assignment between these two.

- Recall: VHDL is strongly-typed language.

- Data objects of <u>different base types</u> CANNOT to assigned to each other without the use of type-conversion.

## Outline

- Basic Structure of a VHDL Module

- ① Library Declaration

- ② Entity Declaration

- ③ Architecture Body

- Data Objects, Identifiers, Types, and Attributes

- Data Objects

- ① Constant

- ② Signal

- ③ Variable

- Data Identifier

- Data Types

- Data Attributes

#### Operators in VHDL

# Attributes (1/2)

- An attribute provides information about items such as entities, architecture, types, and signals.

- There are several useful predefined value, signal, and range attributes (see <u>VHDL Predefined Attributes</u>).

- Example:

type count is integer range 0 to 127; type states is (idle, decision, read, write); type word is array(15 downto 0) of std\_logic;

Then

count'left = 0

states'left = idle

word' left = 15

count'right = 127

states'right = write

word'right = 0

# Attributes (2/2)

- Another important signal attribute is the **`event**.

- This attribute yields a Boolean value of TRUE <u>if an event</u> has just occurred on the signal.

- It is used primarily to determine if a clock has transitioned.

- Example (*more in Lec04*):

• • •

...

if clock = `1' and clock'event then

my\_out <= my\_in;</pre>

## Outline

- Basic Structure of a VHDL Module

- ① Library Declaration

- ② Entity Declaration

- ③ Architecture Body

- Data Objects, Identifiers, Types, and Attributes

- Data Objects

- ① Constant

- ② Signal

- ③ Variable

- Data Identifier

- Data Types

- Data Attributes

#### Operators in VHDL

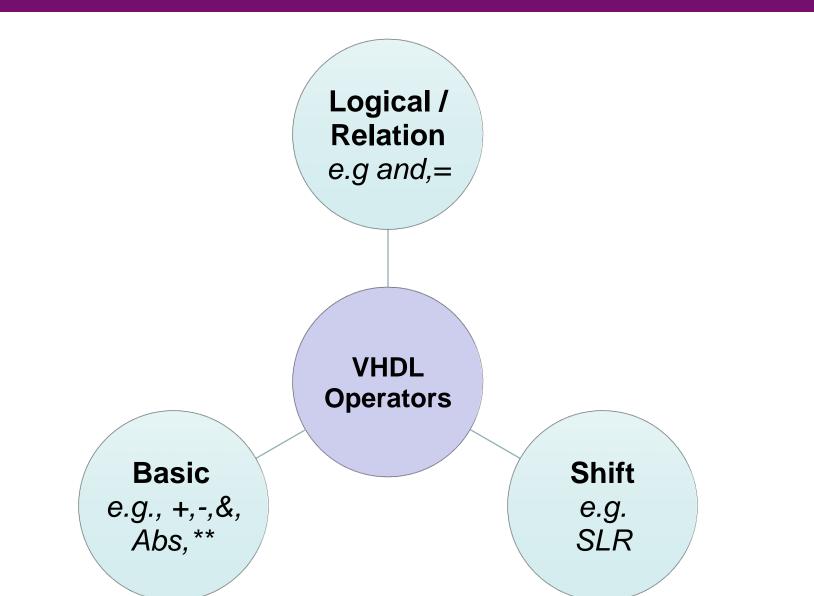

#### **VHDL Operators**

## **Basic Operators**

- + arithmetic add, for integer, float.

- arithmetic subtract, for integer, float.

- multiplication

- / division

- **rem** remainder

- **mod** modulo  $(A \mod B = A (B * N), N \in integer)$

- abs absolute value

- **\*\*** exponentiation (e.g.,  $2^{**3}$  is 8)

- **ଢ** concatenation (e.g., '0' & '1' → "01")

# **Shift / Rotate Operators**

#### Logical Shift and Rotate

- sll shift left logical, fill blank with 0

- srl shift right logical, fill blank with 0

- rol rotate left logical, circular operation

- E.g. "10010101" rol 3 is "10101100"

- ror rotate right logical, circular operation

#### Arithmetic Shift

- **sla** shift left arithmetic, fill blank with 0, same as sll

- sra shift right arithmetic, fill blank with sign bit (MSB)

# Logical / Relation Operators

- Logical Operators: and, or, nand, nor, xor, xnor, not have their usual meanings.

- E.g., nand is NOT associative

- (A nand B) nand  $C \neq A$  nand (B nand C)

- A nand B nand C is illegal

- Relation Operators (result is Boolean)

- = equal

- /= not equal

- < less than

- <= less than or equal

- > greater than

- >= greater than or equal

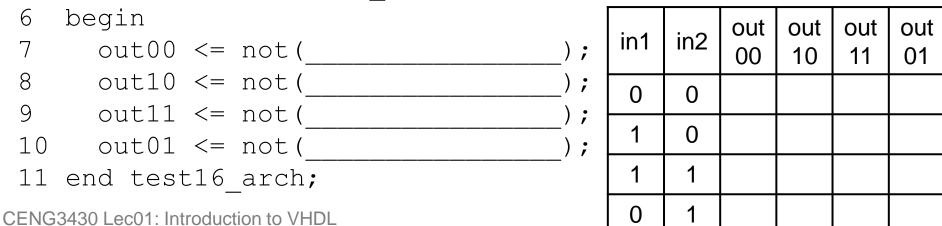

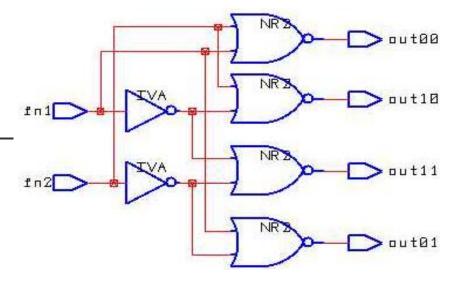

# **Class Exercise 1.8**

Student ID: \_\_\_\_\_ Date: Name:

- Consider the circuit:

- What is this circuit for? Answer: \_\_\_\_\_

- Fill in the truth table.

- Fill in the blanks of code.

```

entity test16 is

1

```

```

port (in1, in2: in std logic;

2

```

out00,out01,out10,out11: out std logic);

```

end test16;

4

```

3

```

5

architecture test16 arch of test16 is

```

# Summary

- Basic Structure of a VHDL Module

- ① Library Declaration

- ② Entity Declaration

- ③ Architecture Body

- Data Objects, Identifiers, Types, and Attributes

- Data Objects

- ① Constant

- ② Signal

- ③ Variable

- Data Identifier

- Data Types

- Data Attributes

- Operators in VHDL

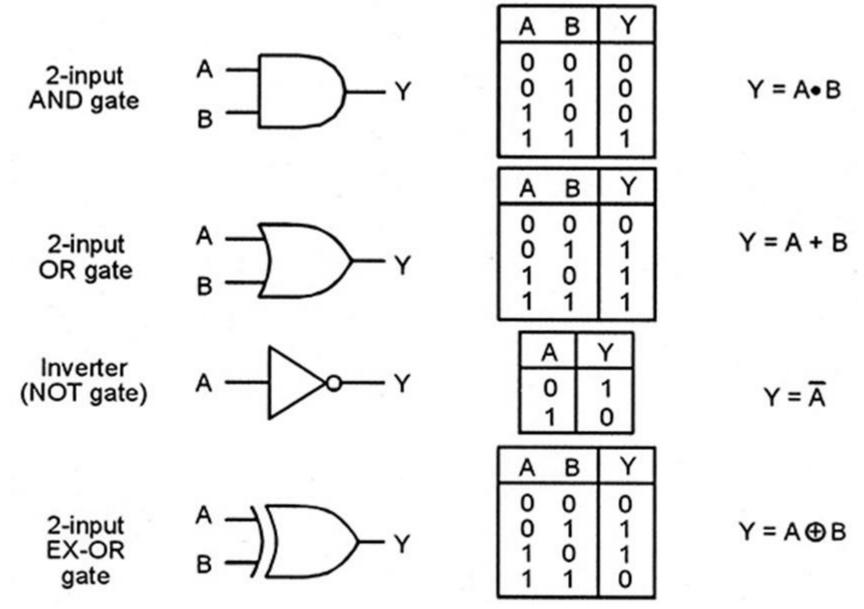

# Review: Basic Gates in Logic Circuits

CENG3430 Lec00: Course Information

62

# **Review: NAND and NOR Gates**

- In many technologies, implementation of NAND gates or NOR gates is easier than that of AND or OR gates.

– NAND Gate:

- gate B

- NOR Gate:

2-input NOR gate

2-input

| А | В | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

$Y = \overline{A + B}$

$Y = A \bullet B$

Any logic function can be realized using <u>only</u> NAND gates or <u>only</u> NOR gates.

CENG3430 Lec00: Course Information

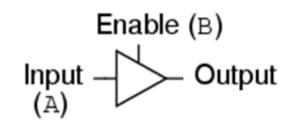

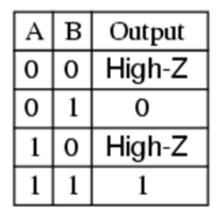

# **Review: Tristate Logic**

- The concept of tristate logic is also essential in digital system designs.

- Directly connecting outputs of two gates together might not operate properly, and might cause damage to the circuit.

- One ways is to use tristate buffers.

- Tristate buffers are gates with a high impedance state (High-Z or Z) in addition to high and low logic states.

- High impedance state is equivalent to an open circuit.

Tristate buffer symbol

CENG3430 Lec00: Course Information

Truth table

(analogy)

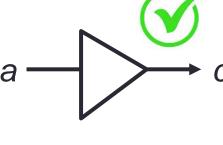

## **Review: Buffer Gate**

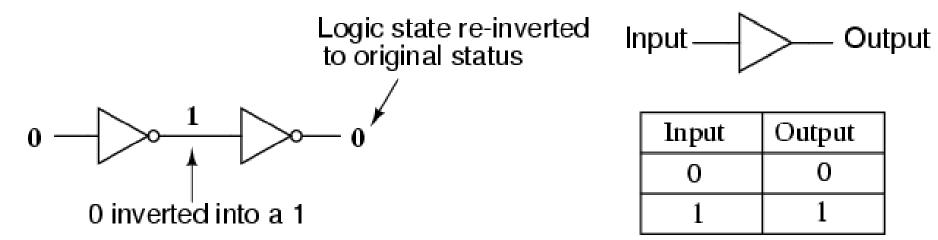

- Double inversion would "cancel" each other out.

- A weak signal may be amplified by means of two inverters.

- For this purpose, a special logic gate called a buffer gate is manufactured to perform the double inversion.

- Its symbol is simply a triangle, with no inverting "bubble" on the output terminal:

Double inversion

"Buffer" gate